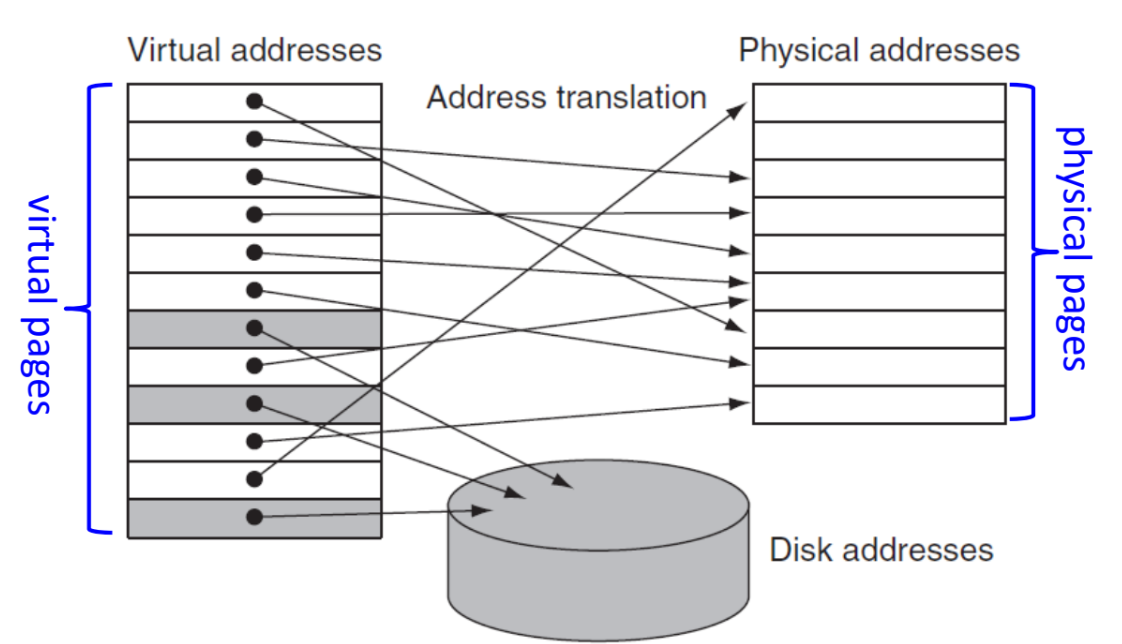

Logical address <-> virtual address

각각의 프로그램은 own address로 실행하고 실시간으로 변환해서 산다.

cache <-> ram 과 비슷한 느낌이다

다만 ram <-> hdd는 그차이가 매우 심하다. 따라서 page fault 날 시에 disk 가야돼서 손해가 매우 큼 -> hit rate를 최대한 올려야한다.

temporal 과 spatial 사이의 적절한 값을 찾아서 page size 결정

fully associative placement 사용

page fault 는 SW로 처리 (hw가 빠르긴하지만 어차피 disk handle 하는데 시간 오래걸려서 SW로 해도 상관없다)

Write-through 보다 당연히 Write-back 사용

Page Table : main memory <-> SW

Page Table Register : Page Table Pointer

만약 한 프로세스의 page table + PC + registers를 다 갖고있다면 언제든지 어디 저장했다가 재실행 가능하다

즉 어떤 process가 실행중이란 말은 특정 process의 page table PC Registers을 사용중이라는 뜻

각 process마다 page table register을 가지고 이걸 이용해서 virtual address를 physical로 전환

운체 내용하고 겹쳐서 간략하게 설명하면 32bit에서 per process당 table size 4MB니까 너무 큼

TLB

SMT급으로 중요한거래유~

page table 활용하면 memory 접근시간 두배걸림.

page table의 locality를 활용해서 TLB만들었다.

TLB 통해서 Physical page address바로 알 수 있다. 이걸로 memory갈수도있고 cache갈수도있고 그런거임

valid : 현재 메모리에 있는지 확인하는 bit. //1이면 memory 0 이면 memory에 없는거

dirty : 1이면 나만 갖고있다. 즉 write back시에 나중에 메모리에도 갱신해라

Ref : 참조bit 참조되었다는거 표시하는 bit인데 교체할때 쓴다.

근데 만약에 TLB miss가 난다? replace 필요하다

TLB는 write back

TLB+Cache

순서 cache는 write though일수도 back일수도있음~

여담 firmware 같은게 os가 아니라 자체 software를가지고 physical하게 접근한다.

따라서 tlb니 vm이런게 없는거

'학교공부 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조 22 - Cache (0) | 2020.06.20 |

|---|---|

| 컴퓨터 구조 21 - Cache (0) | 2020.06.20 |

| 컴퓨터구조 18 - SMT (0) | 2020.06.17 |

| 컴퓨터구조 17 - SMT (0) | 2020.06.17 |

| 컴퓨터구조 16 - Multithreading (1) | 2020.06.17 |