Compiler

: Source program을 Target program으로 변경

보통 c++ java phython과 같은 high level language를 x86 MIPS ARM SPARC 와 같은 기계어로 변역함

설명은 귀찮아서 패스

Registers : 메모리부터 fetch 해온 data stored. cpu는 register하고만 연산

word : 계싼하는 data의 default size

빠르게 MIPS 명령어를 보자

MIPS Instruction Format

32bit 시스템에서임

address = constant 상수가 들어옴

address에 memory address가 와서 번지로 이동함.

MIPS Instruction (refererence)

중요한것만 빠르게 본다. http://www.mrc.uidaho.edu/mrc/people/jff/digital/MIPSir.html

MIPS Instruction Reference

MIPS Instruction Reference This is a description of the MIPS instruction set, their meanings, syntax, semantics, and bit encodings. The syntax given for each instruction refers to the assembly language syntax supported by the MIPS assembler. Hyphens in the

www.mrc.uidaho.edu

ADD $s + $t 더해서 $d 레지스터에 넣어라

advance_pc(4) 는 pc값 4byte 증가시키란 의미로 Jump 말고 그냥 대부분 있는거임

$s에 imm(상수) 값 더해서 t에 저장

만약 int a = b + 4인데 add 쓰면 레지스터 하나 더써야되니까 addi 쓰면 효율적이다.

s와 t 비교해서 같으면 offset만큼 이동하라는 뜻이다.

<<2 가 *4랑 같으니까 offest* 4 byte만큼 이동한다.

branch : conditional Jump

jump : unconditional branch

나머지 BGEZ 나 BGTZ 이렇것도 조건만 다르지 같은 의미

target 주소값으로 이동하는건데 & 연산으로 상위 4bit 가져와서 28bit와 합쳐서 주소만든다. 뒤에가면 배움

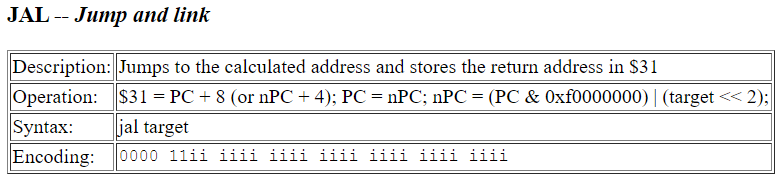

함수콜오면 쓰는 명령어. return address를 31번 레지스터에 저장하는거다. 돌아올때 JR에다가 31번 레지스터 넣어서 돌아옴.

특정 번지수로부터 data를 가져와서 t 레지스터에 넣어라. 메모리부터 data가져올 때 쓰는거.

word단위로 가져옴

MIPS 변환

일단 mips 명령어가 쓰는 레지스터들은 이렇게 각각 종류마다 역할이 정해져있다. 근데 이것대로 지키는건 아니고 바뀌긴도한다는데 암튼 이 규칙을 강하게 지키면서 예제를 풀어보자.

현재 $s에 f g h i j 차곡차곡 넣었다고 생각하면

위의 세가지 동작으로 s0에 계산한 값을 넣을 수 있다.

이번에도 레지스터들에 data는 이미 있는 상태임.

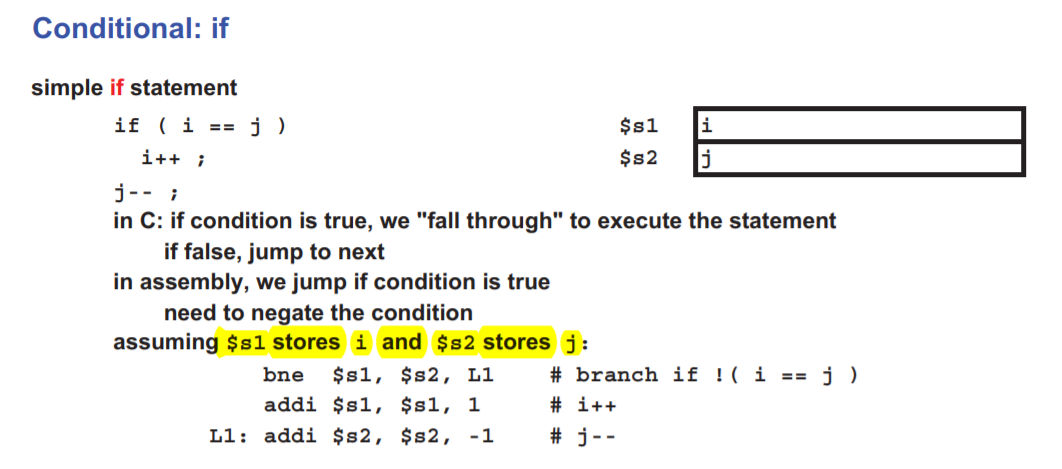

여기서 bne (branch not equal)

i != j 라면 L1으로 jump하라.

만약 jump하면 L1 실행된다.

addi s2 s2 -1 은

s2 = se -1 로 j --를 수행한다.

jump안하면 순차적으로 실행하는거지.

bne imm 주소에 L1인 라벨써도 알아서 가줌 어셈블러도 이정도는 된다 ㅇㅇ

아마 L1은 1일 것이다. (pc+4) + (L1 << 2) PC+4는 무조건 하는거임

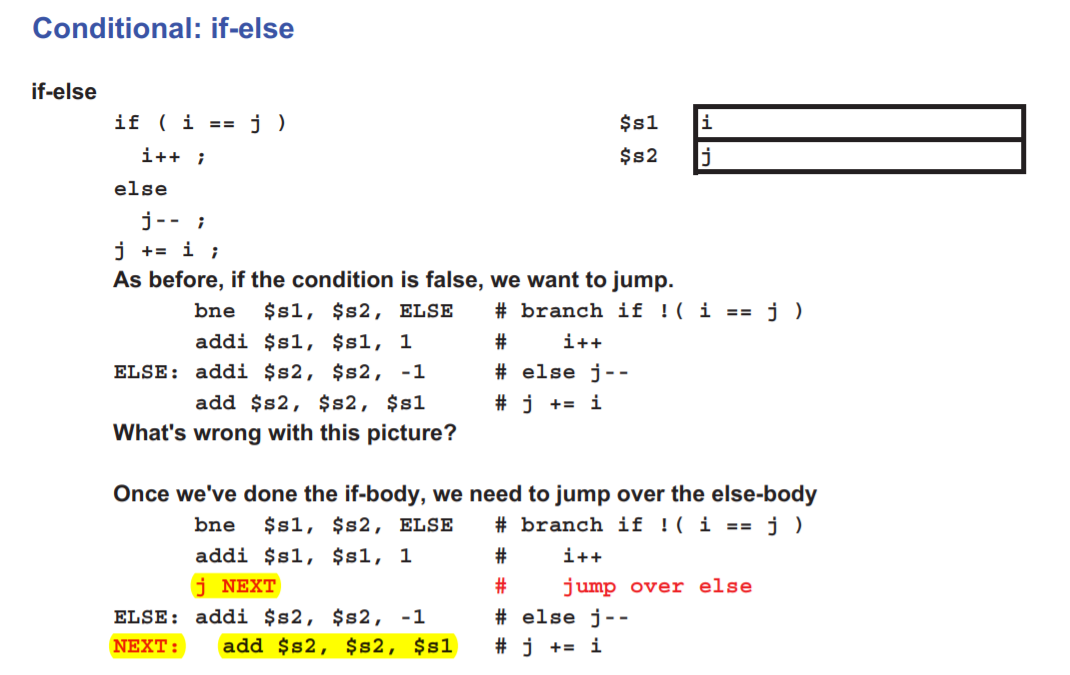

그렇다면 else문 있는건 어떻게 할까?

j NEXT로 가서 else 넘어간다.

ELSE는 offset이니까 2일텐데 jump의 NEXT는 절대 address로 이동한다. 따라서 NEXT라인의 절대주소로 치환될거임

condition이 여러개인 경우는

&&과 ||일 때 달라진다.

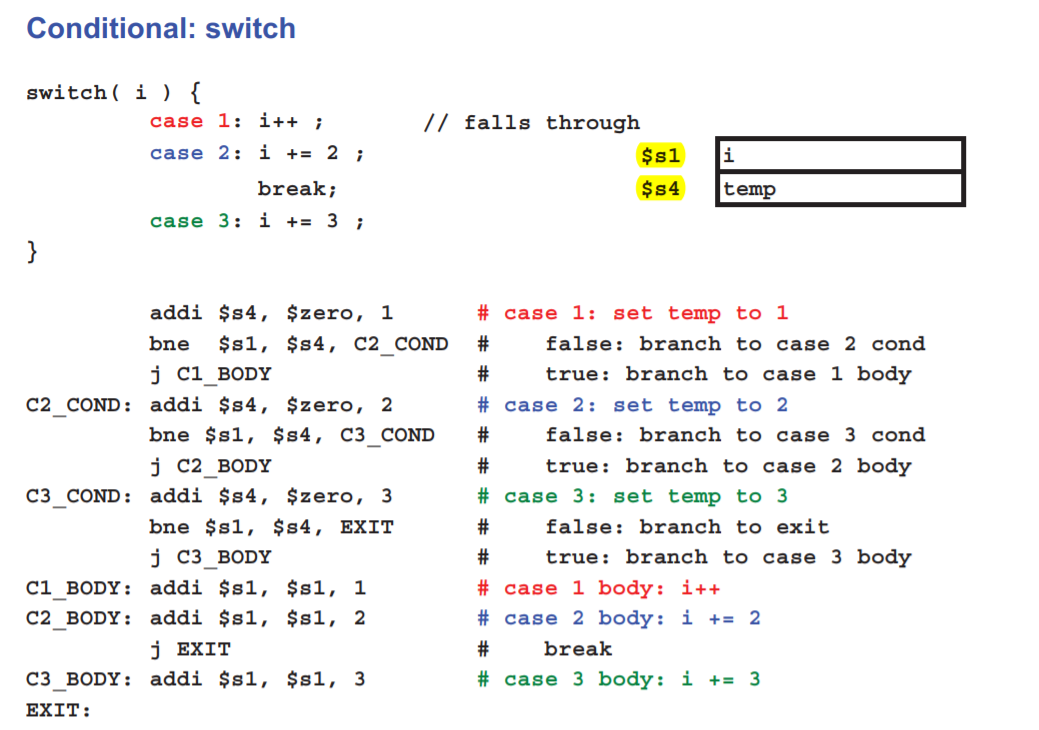

switch문 같은 경우는 모든 case마다 다 bne 때린다

case마다 비교해서 다르면 다음 case로간다. 만족하면 해당 case의 body로 이동.

while문인 경우 if문으로 바꿔서 계산한다.

condition따라 branch사용 여기서는 i<j니까 i >=j (bge greater than or equal)으로 한다.

multiple을 add로 구현한것도 성능상 이득을 위해서임

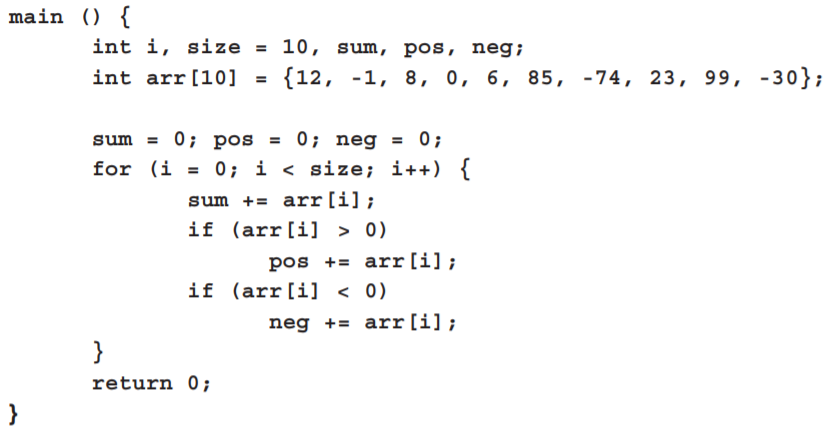

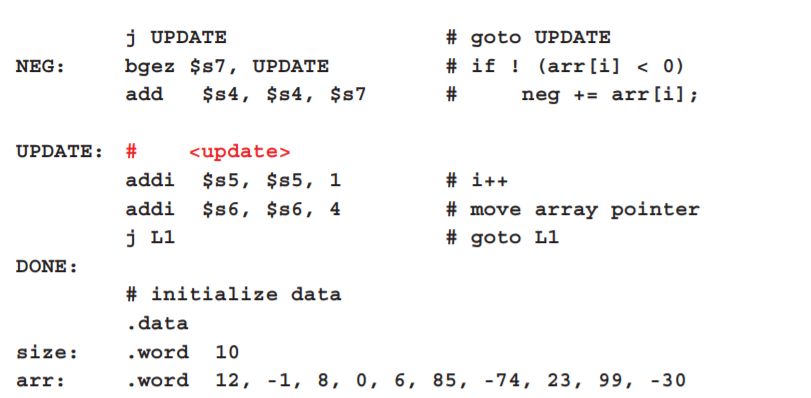

간단한 C 프로그램을 어셈블리어로 변경해보자

한 배열의 합과 양수 합 음수 합 구하는거임

뒤에 .data로 la 와 lw 통해서 초기화 해도돼고 ori ( imm과 rs or 연산해서 rd에 넣음) 통해서 해도 된다.

blez 와 bgez를 통해서 arr[i] 음수 양수 판별 두조건 모두 만족하면 0이니까 바로 UPDATE로 보내버림.

이렇게 MIPS와 C의 교환이 됨.

'학교공부 > 컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조 SingleCycle (0) | 2020.06.15 |

|---|---|

| 컴퓨터구조 MIPS - 2 (0) | 2020.06.14 |

| 컴퓨터구조 Performance (0) | 2020.06.14 |

| 컴퓨터구조 20 - Memory Hierarchy (0) | 2020.05.28 |

| 컴퓨터구조 19 - Memory Hierarchy (0) | 2020.05.20 |